تصاویر معماری Arrow Lake جزئیات طراحی مبتنی بر چیپلت اینتل را نشان می دهد

آندریاس شیلینگ در پلتفرم X (قبلا با نام توییتر شناخته می شد) چندین تصویر از معماری Arrow Lake شرکت اینتل را از نمای نزدیک به اشتراک گذاشته است که طراحی تایل های جداگانه این خط تولید و همچنین چیدمان هسته ها درون تایل های پردازشی را نشان خواهد داد.

جزئیات معماری Arrow Lake شرکت اینتل

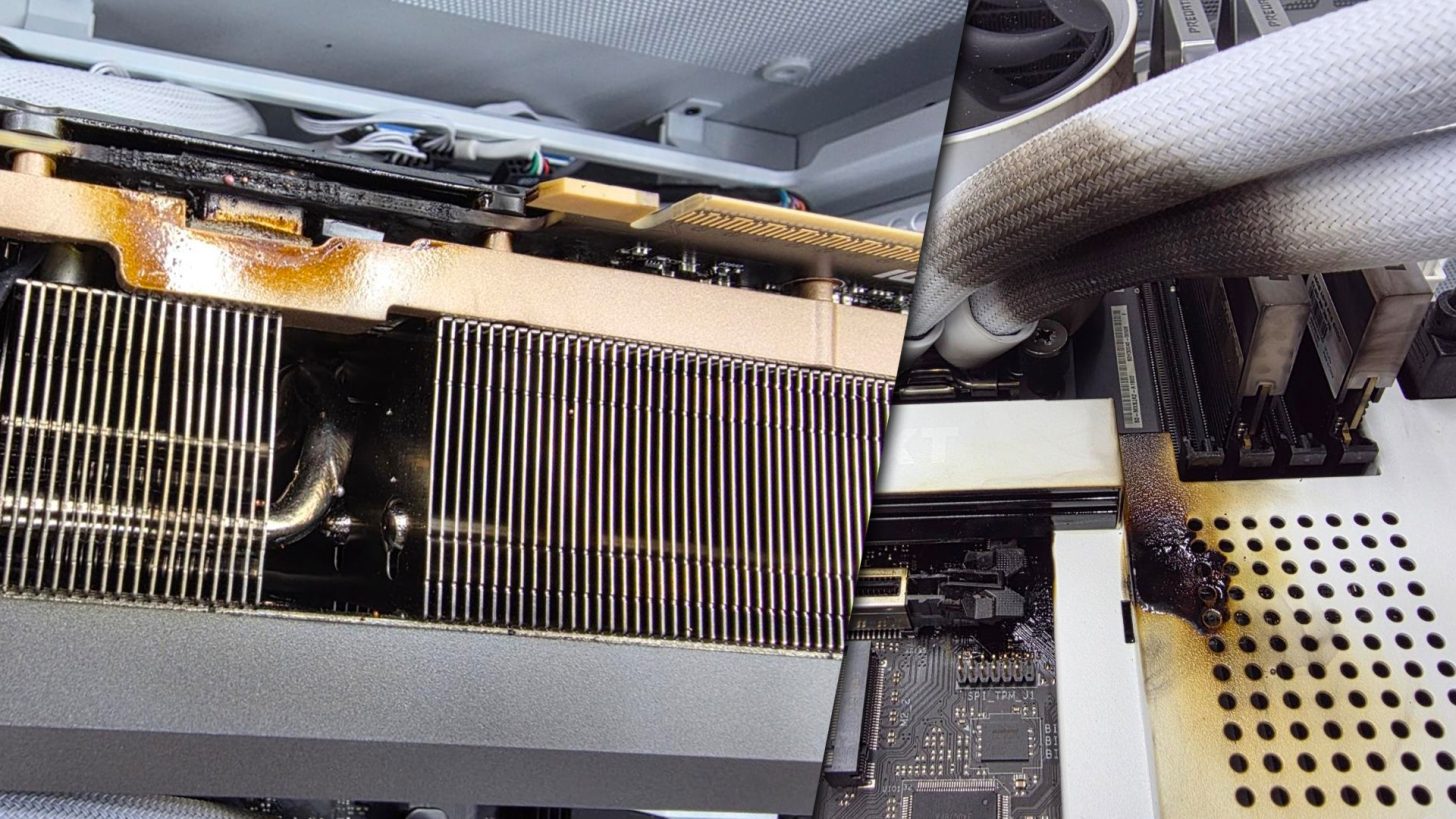

اولین عکس، نمای کامل دای پردازنده های دسکتاپ سری Core Ultra 200S کمپانی اینتل را به نمایش می گذارد، که در آن تایل پردازشی در بالا سمت چپ، تایل I/O در پایین و تایل های SoC و GPU در سمت راست قرار گرفته اند. باید اشاره کرد که در پایین سمت چپ و بالا سمت راست نیز دو دای پرکننده وجود دارد که برای ایجاد استحکام ساختاری طراحی شده اند.

دای پردازشی بر روی گره پیشرفته و مدرن N3B شرکت TSMC با مساحت کلی 117.241 میلی متر مربع ساخته شده است. تایل I/O و تایل SoC بر اساس گره قدیمی تر N6 شرکت TSMC تولید شده اند، همچنین باید گفت که مساحت تایل I/O برابر با 24.475 میلی متر مربع و مساحت تایل SoC برابر با 86.648 میلی متر مربع خواهد بود. تمام این تایل ها بر روی یک تایل پایه زیرین قرار گرفته اند که بر اساس گره 22 نانومتری FinFET کمپانی اینتل ساخته شده است. با این تفاصیل، Arrow Lake اولین معماری شرکت اینتل محسوب می شود که (به جز تایل پایه) کاملاً با استفاده از گره های فرآیند شرکت رقیب تولید شده است.

تصویر بعدی تمام زیرمجموعه تایل های ثانویه در معماری Arrow Lake را نشان می دهد. دای I/O شامل کنترلر تاندربولت 4 / PHY نمایشگر، بافرها/PHYهای PCIe Express و PHYهای TBT4 است. همچنین تایل SoC شامل موتورهای نمایشگر، موتور مدیا، PHYهای PCIe بیشتر، بافرها و کنترلرهای حافظه DDR5 خواهد بود. در نهایت تایل GPU از چهار هسته گرافیکی از نوع Xe و یک اسلایس رندر Xe LPG (Arc Alchemist) پشتیبانی می کند.

پیکربندی هسته معماری جدید کمپانی اینتل

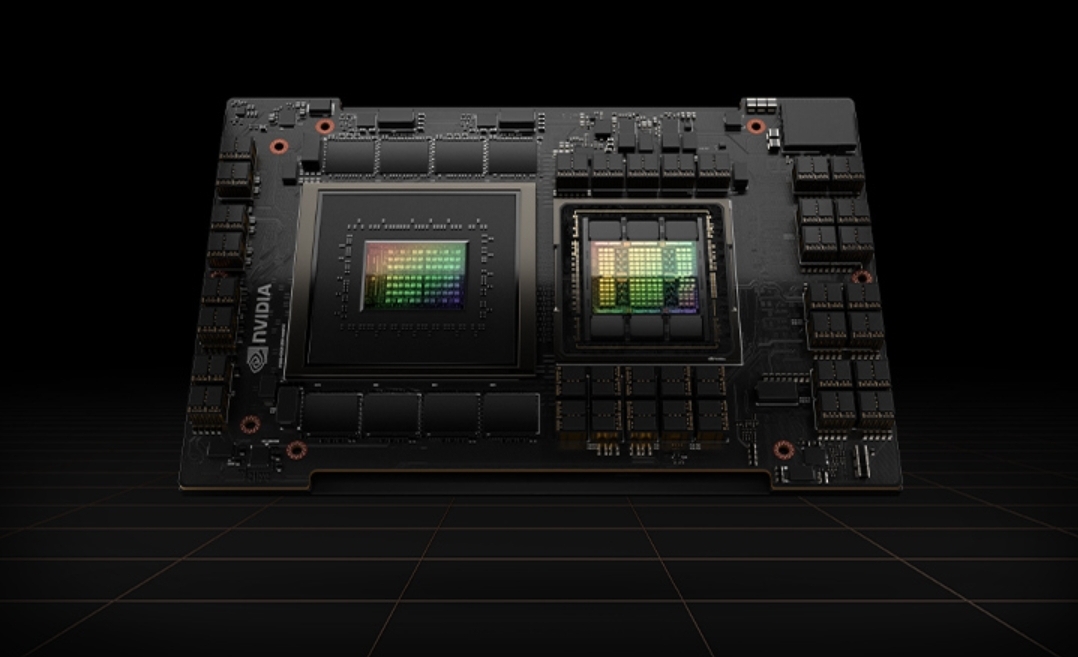

تصویر نهایی جدیدترین پیکربندی هسته کمپانی اینتل برای معماری Arrow Lake را نشان می دهد که با معماری های هایبریدی قبلی این شرکت متفاوت است. کمپانی اینتل تصمیم گرفته است در این پردازنده ها به جای اینکه همه هسته ها را در یک کلاستر مجزا بگذارد، هسته های E را بین هسته های P قرار دهد. به نظر می رسد که این کار برای کاهش نقاط حرارتی انجام شده است. چهار عدد از هشت هسته P در لبه های دای قرار دارند، در حالی که چهار هسته دیگر در وسط دای جای گرفته اند. چهار کلاستر هسته E (که هر کدام شامل چهار هسته هستند) بین هسته های P بیرونی و داخلی دیده می شوند.

تصاویر منتشر شده از سوی شیلینگ چیدمان کش (cache) پردازنده های Arrow Lake را نیز نشان می دهند. بر این اساس، این محصولات از 3 مگابایت کش L3 برای هر هسته P (در مجموع 36 مگابایت) و 3 مگابایت کش L2 برای هر کلاستر هسته E پشتیبانی می کنند، که 1.5 مگابایت آن مستقیماً بین دو هسته مشترک خواهد بود. یک اتصال دهنده دو کلاستر کش L2 (و هسته های مرتبط با آن ها) را به هم متصل می کند، به علاوه مسئول اتصال هر کلاستر هسته به عامل حلقوی (ring agent) نیز خواهد بود. یکی از ارتقاهای اصلی که اینتل در خط تولید Arrow Lake انجام داده، اتصال کلاسترهای هسته E به کش L3 مشترک بین هسته های P است که عملاً به هسته های E نیز کش L3 می دهد.

وضعیت معماری Arrow Lake در بازار دسکتاپ

با این تفاصیل می توان گفت که Arrow Lake یکی از پیچیده ترین معماری هایی محسوب می شود که کمپانی اینتل تا به امروز تولید کرده است. همچنین اولین معماری این شرکت است که طراحی مبتنی بر چیپلت را به بازار دسکتاپ می آورد. با این حال، اولین تلاش اینتل برای ساخت یک طراحی مبتنی بر چیپلت برای بازار دسکتاپ، به دلیل بروز مشکلات تأخیر (latency) ناشی از اینترکانکت که مسئول اتصال تمام تایل ها به یکدیگر است، به خوبی مورد استقبال قرار نگرفت. اینتل در تلاش است این مشکل را از طریق انتشار آپدیت های فریمور (firmware) برطرف کند. با این حال، پیاده سازی فعلی این معماری نمی تواند با پردازنده های ساخته شده توسط شرکت AMD، یعنی سری Ryzen 9000 (مانند نسخه 9800X3D) رقابت کند. باید گفت که این محصولات حتی برای شکست دادن پردازنده های نسل قبلی خود شرکت اینتل (مانند نسخه 14900K) نیز قدرتمند نیستند.

با این اوصاف، حرکت به سمت رویکرد چیپلت راه های بیشتری را برای کمپانی اینتل فراهم می کند تا معماری های خود را در آینده به شیوه ای کارآمدتری بهینه سازی کند. هر تایل می تواند مستقلاً از تایل های دیگر توسعه یابد و بر اساس گره های متفاوت تولید شود. به این ترتیب بازده تولید بهبود می یابد، توسعه بهینه سازی می شود و در نهایت هزینه های تولید کاهش پیدا خواهند کرد.

بدون امتیاز

کمی صبر کنید…